Now you can run the test and check the result in /path/to/simulation/folder/my_reg_model.xml.

call of the export to ipxact on your instance of the register model Reg_block = env.reg_agent.reg_model_inst

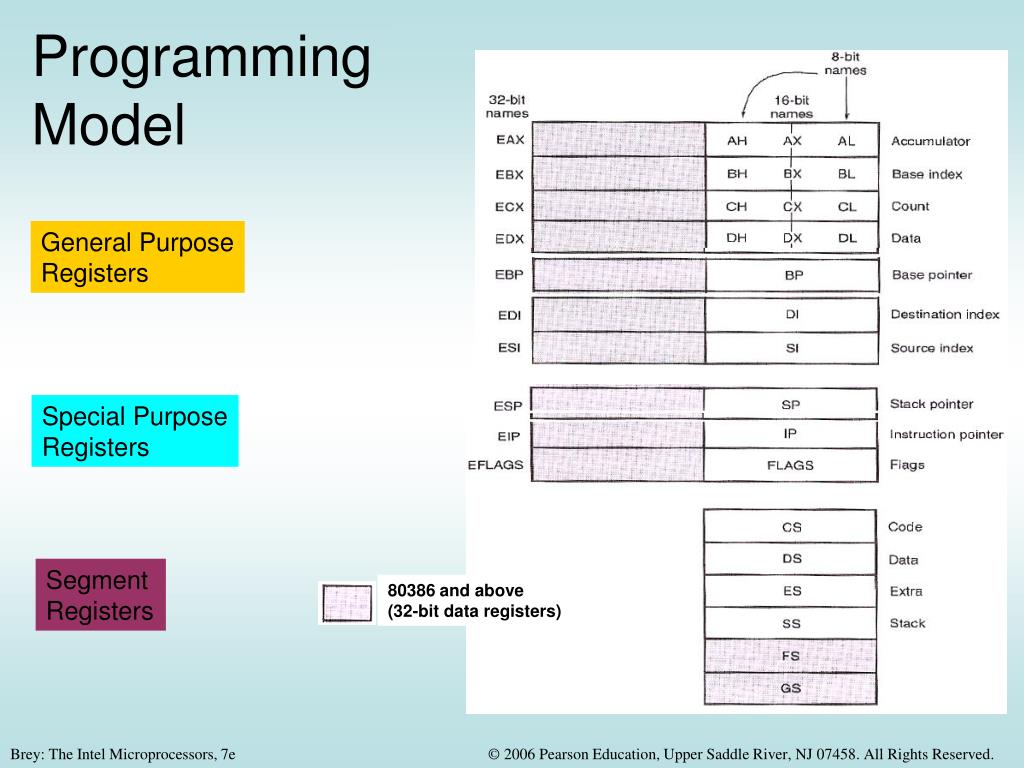

somehow get the pointer to the register model instance Modify here the parameters with the ones desired.īasic_t_parameters("ipxact.xml", "avendor", "alibrary" In the run phase of the test include the following code: virtual task run_phase(uvm_phase phase) īasic_printer = uvm_reg_to_ipxact_printer::type_id::create("basic") Make sure you include uvm_reg_to_ipxact_pkg.sv in the compile flow of your verification environment and import it in the test: import uvm_reg_to_ipxact_pkg::* You can follow the steps bellow if you already have a working register model and test that uses it. How to export your register model using an existing test Now you can run the application by using one of the demo run scripts and check the result in /path/to/uvm_reg_to_ipxact/scripts/xml/my_reg_model.xml. Modify the global parameters of the IP-XACT model: // See documentation for more detailsīasic_t_parameters("my_reg_model.xml", "me", "my_reg_library" Reg_block = my_reg_block::type_id::create("basic_block") Make sure you include your register model files in the testbench: `include "my_reg_file.sv"Ĭreate an instance of your register model in the initial-task: initial begin How to export your register model using the demo testbench Running the above command will generate an xml file under /path/to/uvm_reg_to_ipxact/scripts/xml/. IEEE 1685, “Standard for IP-XACT, Standard Structure for Packaging, Integrating and Re-Using IP Within Tool-Flows,” describes an XML Schema for meta-data documenting Intellectual Property (IP) used in the development, implementation and verification of electronic systems and an Application Programming Interface (API) to provide tool access to the meta-data. Here is a thorough presentation for the UVM_REG model. UVM_REG is an abstract SystemVerilog model for registers and memories from the DUT. The application is available for free under the Apache License 2 and it can be downloaded from GitHub uvm_reg_to_ipxact repository. You can use this application to generate IP-XACT models from existing UVM register models in order to ease IP-XACT adoption. This post presents a simple application for exporting existing UVM/SystemVerilog register models to an IP-XACT file.

0 kommentar(er)

0 kommentar(er)